上海交大郭鑫斐团队研究成果获IEEE国际会议最佳论文奖

近日,上海交通大学密西根学院助理教授郭鑫斐课题组发表的题为《RECO-HCON: A High-Throughput Reconfigurable Compact ASCON Processor for Trusted IoT》的研究论文在英国举行的第三十五届IEEE片上系统国际会议中从众多优秀论文中脱颖而出,获颁大会唯一最佳论文奖(Best Paper Award)。郭鑫斐为论文通讯作者,学院22届本科毕业生魏翔东为共同第一作者、朱正平为第三作者。论文项目合作方包括美国加州州立理工大学和伊利诺伊大学。

物联网(IoT)安全一直是行业内和学术界关注的焦点,据统计,到2030年,全球将会有超过254亿台物联网设备。当前,物联网设备已用于各个行业,包括制造、汽车、医疗、能源等,而根据其特定的应用场景,物联网芯片的规模已涵盖了最简单的传感器采样电路到微处理器乃至大型的片上系统(System on Chip)。物联网芯片组成智能设备网络,它们相互连接,在数据传输过程中极其容易受到攻击而引发安全漏洞,而终端类型繁多、接入方式多样、业务场景丰富且应用场景复杂,因此很难设计具有扩展性的硬件加密认证模块而赋能可信物联网。

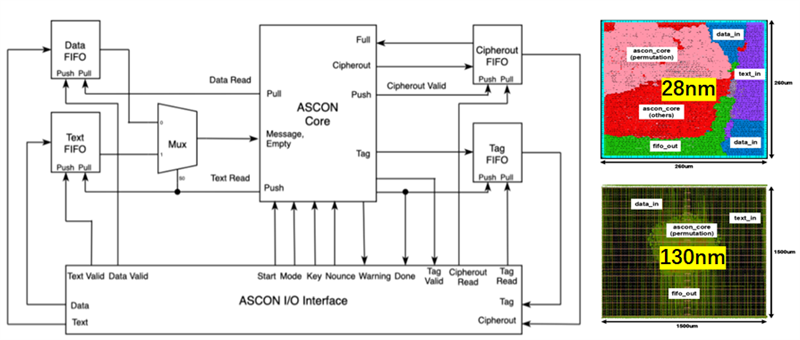

本文所提出的新型可重构ASCON安全处理架构以及其在两个工艺节点的硬件实现

针对这一问题,本论文提出了一种新型的基于ASCON算法的加密硬件架构,具有极高的可扩展性和可重构性,从而可以适配多种物联网使用场景。ASCON是美国国家标准与技术研究院于2013年提出的加密算法竞赛的CAESAR(The Competition for Authenticated Encryption: Security, Applicability, and Robustness)竞赛的最终入围算法之一,被选为轻量级认证加密的“主要代表”。本项目在该算法的基础上,在架构层面进行了深度扩展和优化,除了支持加密、解密,还支持哈希函数等六种模式,通过用Chisel设计语言和敏捷设计方法实现,最终在28纳米和130纳米两种工艺和两种设计流程下进行了性能、功耗和面积的多方面验证,相比最新的工作,本文所提出的设计支持6个以上模式,吞吐量(单位:Gb/s)在不同模式下均高于同类单一模式设计并超过50%,而能耗则比类似设计低至少一个数量级,可以满足纽扣电池供电的物联网设备不间断使用超过30天。另外通过在开源EDA工具链OpenLane中的实现,本文提出的设计将支持端到端的全流程开源,满足更多开发者的需求。

最佳论文奖获奖证书

项目成员加州州立理工大学Mohamed El-Hadedy教授代表团队在大会现场领奖

背景介绍:

IEEE片上系统国际会议

IEEE片上系统国际会议(IEEE International System-on-Chip Conference,SOCC)一直是分享片上系统(SoC)体系结构、系统、逻辑和电路设计、工艺技术、测试、设计工具和应用方面最新进展的主要国际论坛,由电路与系统学会主办,今年是大会举办的第35届,吸引了包括英伟达公司首席技术官、图灵奖获得者等多位业界和学术界专家学者参会和分享最新的进展,大会接收了60余篇高质量论文,会程共3天,包括4个主题演讲,8个口头和海报展示,7个工业界热点专题讨论会以及4个领域专家举办的特别专题和圆桌会议。

作者简介

魏翔东,上海交通大学密西根学院2022届本科毕业生,目前已开始在美国密西根大学攻读电子与计算机工程博士学位。

郭鑫斐,上海交通大学密西根学院长聘教轨助理教授,博士生导师,IEEE高级会员。博士毕业于弗吉尼亚大学计算机工程系,硕士毕业于佛罗里达大学电子与计算机工程系,曾任职于英伟达、IBM,作为主要贡献者参与了包括业界领先的第二代和第三代BlueField系列数据处理器DPU等多个芯片产品的研发工作,主持或参与芯片流片7颗,囊括从180nm到7nm的多个工艺节点,在集成电路设计、EDA和FPGA等领域会议期刊发表论文40余篇,出版著作1本,获得4次最佳论文、专题奖。目前担任期刊Integration, the VLSI Journal的编委,担任30多个领域内顶级会议的程序委员会成员,如DAC、ICCAD、CICC、FCCM、HOST等,同时担任CCF开源发展委员会、容错专委执行委员。目前主要研究兴趣是低功耗高可靠性数字电路和系统、机器学习辅助EDA技术和可重构计算。

智能电路、架构和系统实验室(iCAS)

实验室拟通过科研的形式解决目前数字芯片设计中最为棘手和挑战的问题。目前的科研领域跨越电路设计、体系和系统层次,主要集中于两个方向,第一个方向为通过利用人工智能和机器学习的手段辅助设计芯片,第二个方向为如何设计能耗和可靠性最优的智能芯片。实验室课题涉及跨层级协同设计、机器学习与硬件的结合、低功耗电路设计以及新型体系架构。iCAS探索芯片设计的多个设计瓶颈,通过开发多种设计方法不断突破瓶颈,最终目标是设计最优的芯片满足日益增长的计算需求。实验室网站见:https://sites.ji.sjtu.edu.cn/icas。

【免责申明】本专题图片均来源于学校官网或互联网,若有侵权请联系400-0815-589删除。