精仪系类脑计算团队在新型器件技术上取得进展

在过去半个多世纪里,集成电路产业一直在晶体管微缩驱动下发展(“摩尔定律”)。然而,随着晶体管尺寸微缩难度的持续增加,性能提升的空间不断缩小,集成电路的发展逐渐进入“后摩尔”时代。在“后摩尔”时代,新型器件和电路功能将成为主要驱动力。

基于阻变器件的神经形态硬件是后摩尔时代新型技术的代表,具有类神经网络功能、存算一体和大规模并行计算的独特优势,有望突破冯·诺伊曼架构的固有瓶颈。长期以来,阻变器件面临着“电流-保留时间”的矛盾,即受限于金属导电细丝的固有特性,阻变器件状态的保留时间与操作电流成正相关关系,这恰好与其实际使用需求相违背:长期非易失存储功能需要在较低的电流下实现以保证能耗优势,而短期易失选通功能则需要较大的打开电流来保证读出裕度。

针对上述问题,清华大学精密仪器系类脑计算团队提出基础单质半导体碲(Te)导电细丝的新型阻变器件技术,通过Te半导体导电细丝的生长/断裂实现器件的高/低电导切换。

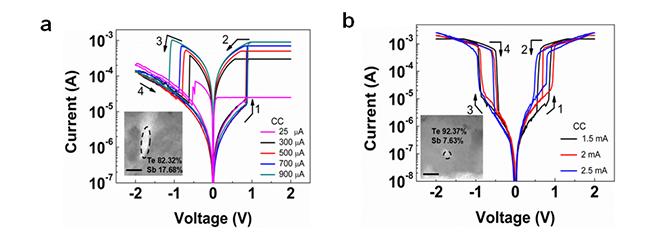

图1:Te导电细丝阻变器件的阻变特性曲线和Te细丝透射电子显微图像

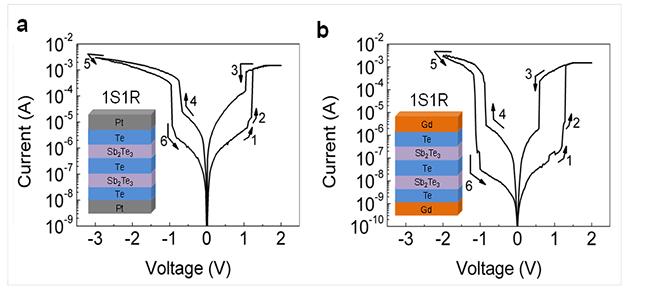

该设计利用Te半导体材料具有电化学活性、低熔点,低导热系数和低电导率的特点,反转了阻变器件状态的保留时间与操作电流的依赖关系。在微米尺度的器件里,长期非易失存储模式的操作电流可以低至几个微安量级(在纳米尺度的器件里可低至几十皮安),而短期易失选通模式的操作电流可以达到几个毫安量级。“电流-保留时间”关系的反转与Te导电细丝的使用密不可分:电化学生成的Te导电细丝相比于金属导电细丝电阻更大,相同电压下器件电流更低(低电导);而在更大的电流下,Te导电细丝容易聚集焦耳热(低热导),使局部最高温度超过Te熔点(低熔点),从而使导电细丝再度被熔断,形成短期易失特性。这一性能成功破解了传统阻变器件中普遍面临的“电流-保留时间”矛盾,在同一个单器件上同时实现了能满足应用需要的存储和选通两种功能,并演示了“存储-选通”单元同质集成的可能性。

由于Te特有的电学-热学性质组合,利用Te导电细丝的阻变器件具有较大且独特的潜在优化空间,如电介质热导率优化、保护电极的功函数、电负性优化等。

图2:基于Te导电细丝的同质集成1S1R单元及其阻变性能曲线

该研究成果近日以“半导体碲的新机遇:阻变器件制备”(A new opportunity for the emerging tellurium semiconductor: making resistive switching devices)为题,发表在《自然·通讯》(Nature Communications)上。

清华大学精密仪器系2018级博士生杨逸飞、徐明坤和复旦大学芯片与系统前沿技术研究院博士后贾淑静为本文的共同第一作者。清华大学精密仪器系李黄龙副教授、裴京副研究员,机械工程系刘大猛副教授和北京信息科技大学段文睿讲师为该文的共同通讯作者,该研究得到了国家自然科学基金、中国科协青年人才托举工程、北京市脑科学与类脑研究中心、科技部重点专项、北京市重大专项等的资助。

该项成果是近年来精仪系类脑计算团队在类脑硬件方面所取得的又一项原创性成果。2014年9月,由精仪系类脑计算团队发起,联合了清华大学校内七个院系组成了清华大学类脑计算研究中心(以下简称“中心”),是国内最早进行全方位类脑智能研究的中心,涉及类脑计算模型和算法、类脑计算芯片、类脑计算软件、类脑计算系统和应用等多个层面。

近年来,中心在类脑计算领域取得了一系列先进成果:2015年研发了第一代芯片类脑芯片——Tianjic®芯片,是世界上首款异构融合芯片,可同时运行人工神经网络(ANNs)和脉冲神经网络(SNNs);2017年发展了基于28纳米的第二代Tianjic®芯片;天机芯片异构融合架构相关成果于2019年被《自然》(Nature)期刊以封面形式报道,同年入选科技部评选的“十大科学进展”和世界互联网大会评选的“领先科技成果”。中心注重类脑计算科技成果的产业化,不断探索新型的类脑计算产学研模式。发起国际大学生类脑计算大赛并连续三年主办(2017-2019);于2018年孵化了北京灵汐科技有限公司(国家高新技术企业、中关村颠覆性创新企业);于2020年发起成立清华大学-中电海康集团有限公司类脑计算联合研究中心。目前,中心已经研发出第三代Tianjic芯片,可运行更大更深更复杂的人工神经网络和脉冲神经网络架构,并已经进入产业化应用阶段。

文章链接:

https://doi.org/10.1038/s41467-021-26399-1

【免责申明】本专题图片均来源于学校官网或互联网,若有侵权请联系400-0815-589删除。